Hi

I don’t have doppler board but

I can to say that in the FPGA community I am in,

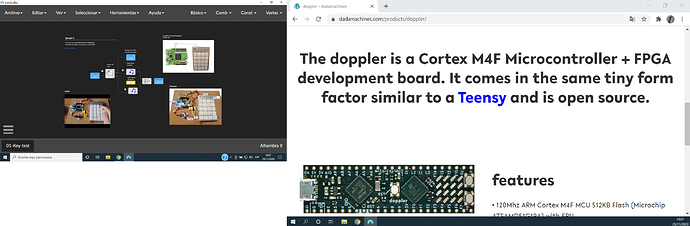

we have the open source programme

ICESTUDIO supports many FPGAs.

does everything visually.

From a block diagram, a file will be generated and automatically loaded into the FPGA.

You don’t need to program any verilog,

if you outline you can do it with the blocks

existing.

Although logically you can generate your own blocks and add the verilog code to perform the specific task.

I leave the links for you to try.

Good luck

https://github.com/FPGAwars/icestudio